# 第2章

## 组合电路Verilog设计

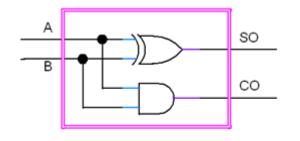

### 2.1.1 半加器的数据流建模描述方式

| A | В | so | CO |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 1 | 1  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | 1  |

|   |   |    |    |

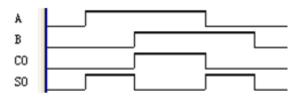

图 2-1 半加器的电路结构

图 2-2 半加器的真值表

图 2-3 半加器的仿真功能波形图

$SO = A \oplus B$  ;  $CO = A \cdot B$

2.1.1 半加器的数据流建模描述方式

```

[例 2-1]

module h_adder (A,B,SO,CO);

input A,B;

output SO,CO;

assign SO = A ^ B;

assign CO = A & B;

endmodule

```

- 2.1.1 半加器的数据流建模描述方式

- 1. 模块语句及其表达方式

module 模块名 (模块端口名表); 模块端口和模块功能描述。

endmodule

2. 端口语句、端口信号名和端口模式

```

input 端口名1,端口名2,...;

(1) input : 输入端口。

output 端口名1,端口名2,...;

(2) output : 输出端口。

input [msb: lsb] 端口名1,端口名2,...;

(3) inout : 双向端口。

```

module h adder (input A, input B, output SO, output CO);

- 2.1.1 半加器的数据流建模描述方式

- 1. 模块语句及其表达方式

```

module 模块名 (模块端口名表);

模块端口和模块功能描述。

```

endmodule

2. 端口语句、端口信号名和端口模式

```

input 端口名 1,端口名 2,...;

output 端口名 1,端口名 2,...;

inout 端口名 1,端口名 2,...;

input [msb:lsb] 端口名 1,端口名 2,...;

```

- 2.1.1 半加器的数据流建模描述方式

- 3. 逻辑操作符

逻辑与"&"和逻辑异或"^"

4. 连续赋值语句

assign 目标变量名 = 驱动表达式; assign [延时] 目标变量名 = 驱动表达式; assign #6 R1 = A & B; `timescale 10ns/100ps

- 5. 关键字

- 6. 标识符

### 2.1.2 半加器的门级原语和UDP结构建模描述方式

| 【例 2-2】                                                                         | 【例 2-3】                                                                                                                   |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| <pre>primitive XOR2(DOUT, X1, X2); input X1, X2; output DOUT; table // X1</pre> | module H_ADDER (A,B,SO,CO) ; input A,B; output SO,CO; XOR2 U1(SO,A,B); // 调用元件 XOR2 and U2(CO,A,B); // 调用元件 and endmodule |

- 2.1.2 半加器的门级原语和UDP结构建模描述方式

- 1. 库元件及其调用

- 2. 用户自定义原语

- 3. 注释符号

- 4. 规范的程序书写格式

- 5. 文件取名和存盘

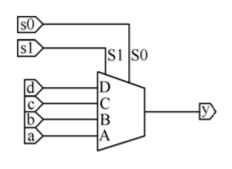

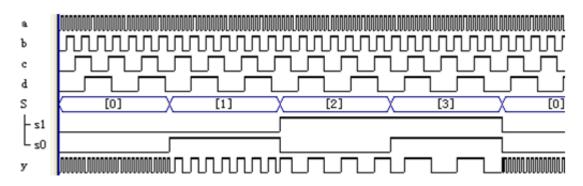

### 2.2.1 4选1多路选择器及其顺序语句表述方式

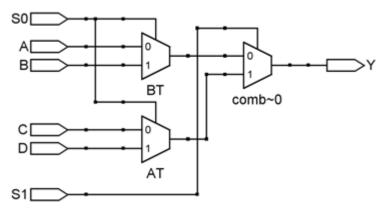

图 2-4 4 选 1 多路选择器

图 2-5 4 选 1 多路选择器 MUX41a 的时序波形

2.2.1 4选1多路选择器及其顺序语句表述方式

```

【例 2-4】

```

end

2.2.1 4选1多路选择器及其顺序语句表述方式

3. 块语句begin \_end begin \_end 块语句的一般格式如下:

```

begin [: 块名]

语句 1; 语句 2; . . .; 语句 n;

end

```

- 2.2.1 4选1多路选择器及其顺序语句表述方式

- 4. case条件语句

case (表达式)

取值 1 : begin 语句 1; 语句 2; ...; 语句 n; end

取值 2 : begin 语句 n+1; 语句 n+2; ... 语句 n+m; end

...

default: begin 语句 n+m+1; ...; end

endcase

5. Verilog的4种逻辑状态

1、0、z和x

- 2.2.1 4选1多路选择器及其顺序语句表述方式

- 6. 并位操作运算符

$\{a1, b1, 4\{a2,b2\}\}=\{a1, b1, \{a2,b2\}, \{a2,b2\}, \{a2,b2\}, \{a2,b2\}\}=\{a1,b1,a2,b2,a2,b2,a2,b2,a2,b2\}$

7. Verilog的数字表达形式

<位宽> '<进制> <数字>

2.2.2 4选1多路选择器及其并行语句表述方式

#### 【例 2-5】

- 2.2.2 4选1多路选择器及其并行语句表述方式

- 1. 按位逻辑操作符

表 2-1 逻辑操作符

| 逻辑功能 | A,B逻辑操作结果                                | C,D 逻辑操作结果                                                                                      | C,E 逻辑操作结果                                                                                                                                                               |

|------|------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 逻辑取反 | ~A= <u>1'</u> b1                         | $\sim$ C = 4.7b0011                                                                             | $\sim$ E = 6. b101001                                                                                                                                                    |

| 逻辑或  | $A \mid B = 1'b 1$                       | $C \mid D = 4.5b1111$                                                                           | $C \mid E = 6.6 \times b0111110$                                                                                                                                         |

| 逻辑与  | A & B = 1' b 0                           | C & D = 4.5b1000                                                                                | C & E = 6'b000100                                                                                                                                                        |

| 逻辑异或 | $A \wedge B = \underline{1}' b 1$        | $C \wedge D = 4.5b0111$                                                                         | $C \wedge E = 6'b011010$                                                                                                                                                 |

| 逻辑同或 | $A \sim^{\wedge} B = \underline{1'} b 0$ | $C \sim^{\wedge} D = 4.5000$                                                                    | C ~^ E = <u>6</u> . b100101                                                                                                                                              |

|      | 逻辑取反<br>逻辑或<br>逻辑与<br>逻辑异或               | 逻辑取反     ~A = 1'b1       逻辑或     A B = 1'b 1       逻辑与     A&B = 1'b0       逻辑异或     A^B = 1'b1 | 逻辑取反     ~A = 1'b1     ~C = 4'b0011       逻辑或     A B = 1'b 1     C D = 4'b1111       逻辑与     A&B = 1'b 0     C&D = 4'b1000       逻辑异或     A^B = 1'b 1     C^D = 4'b0111 |

设: A=1'b0; B=1'b1; C[3:0]=4'b1100; D[3:0]=4'b1011; E[5:0]=6'b010110;

- 2.2.2 4选1多路选择器及其并行语句表述方式

- 2. 等式操作符

表 2-2 等式操作符

| * * * * * * * * * * * * * * * * * * * * |     |                                              |

|-----------------------------------------|-----|----------------------------------------------|

| 等式操作符                                   | 含义  | 等式操作示例                                       |

| ==                                      | 等于  | (3==4)= 0; (A==4'b1011)= 1; (B==4'b1011) =0; |

| !=                                      | 不等于 | (D!=C) = 1; (3!=4) = 1;                      |

| ===                                     | 全等  | (D===C) = 1 ; (E===4'b0x10) = 0 ;            |

| !==                                     | 不全等 | (E===4.60x10) = 1;                           |

设: A=5'b01011; B=4'b0010; C=4'b0z10; D=4'b0z10; E=3'bx10

- 2.2.2 4选1多路选择器及其并行语句表述方式

- 3. wire定义网线型变量

```

wire 变量名 1, 变量名 2, . . . ;

wire [msb:lsb] 变量名 1, 变量名 2, . . . ;

wire a1, a2;

assign Y = a1 ^ a2;

```

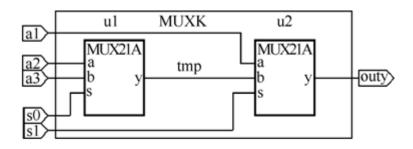

### 2.2.3 4选1多路选择器及其条件操作语句表述方式

#### 【例 2-6】

```

module MUX41a (A,B,C,D,S1,S0,Y);

input A,B,C,D,S1,S0;

output Y;

//若S0=1, 则AT=D; 若S0=0, 则AT=C

wire AT = S0 ? D : C;

//若S0=1, 则BT=B; 若S0=0, 则BT=A

wire BT = S0 ? B : A;

//若S1=1, 则Y=AT; 若S1=0, 则Y=BT

wire Y = (S1 ? AT : BT);

endmodule

```

图 2-6 例 2-6 的 RTL 图

2.2.4 4选1多路选择器及其条件语句表述方式

#### 【例 2-7】

- 2.2.4 4选1多路选择器及其条件语句表述方式

- 1. if\_else条件语句

```

if (S) Y = A; else Y = B; if (S) Y=A; else begin Y=B; Z=C; Q=1/b0; end

```

- 2. 过程赋值语句

- (1) 阻塞式赋值。

- (2) 非阻塞式赋值。

- 3. 数据类型表示方式

#### 2.2.5 4选1多路选择器及其利用UDP元件的结构表述方式

```

【例 2-8】

【例 2-9】

primitive

module MUX41UDP (D,S,DOUT) ;

MUX41 UDP(Y,D3,D2,D1,D0,S1,S0);

input [3:0] D;

input D3,D2,D1,D0,S1,S0; output Y;

input [1:0] S;

table //D3 D2 D1 D0 S1 S0 : Y

output DOUT;

? ? 1 0 0 : 1;

MUX41 UDP (DOUT, D[3], D[2],

? ? 0 0 0 : 0;

D[1],D[0],S[1],S[0]);

? ? 1 ? 0 1 : 1;

? ? 0 ? 0 1 : 0;

endmodule

? 1 ? ? 1 0 : 1;

? 0 ? ? 1 0 : 0;

1 ? ? ? 1 1 : 1;

0 ? ? ? 1 1 : 0;

endtable

endprimitive

```

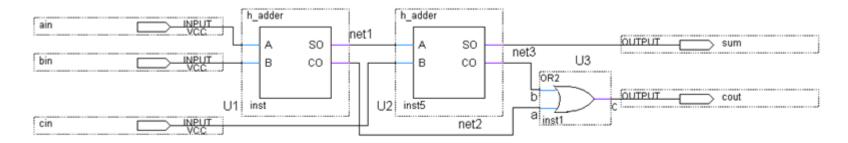

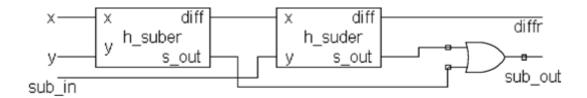

- 2.3.1 全加器设计及例化语句应用

- 1. 全加器原理图结构

图 2-7 全加器 f\_adder 电路图

- 2.3.1 全加器设计及例化语句应用

- 2. 全加器顶层设计文件

【例 2-10】//全加器顶层设计描述

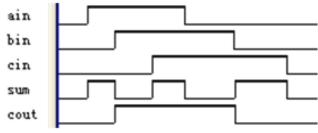

图 2-8 全加器仿真时序

- 2.3.1 全加器设计及例化语句应用

- 3. Verilog例化语句应用方法

```

<模块元件名> <例化元件名> ( .例化元件端口(例化元件外接端口名),...);

h_adder U2(.A(net1), .SO(sum), .B(cin),.CO(net3));

h_adder U2(.B(cin), .CO(net3), .A(net1), .SO(sum));

h_adder U1( ain, bin, net1, net2);

```

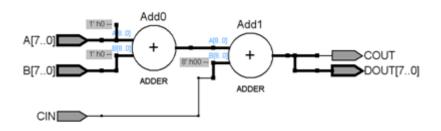

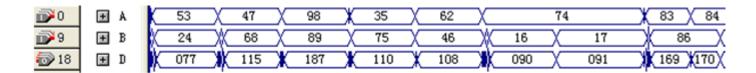

#### 2.3.2 8位加法器设计及算术操作符应用

```

【例 2-11】

【例 2-12】

module

module

ADDER8B(A,B,CIN,COUT,DOUT);

ADDER8B (A,B,CIN,COUT,DOUT);

output[7:0] DOUT; output COUT;

output [7:0] DOUT;

input[7:0] A,B; input CIN;

output COUT;

wire [8:0] DATA;

input [7:0] A,B;

//加操作的进位自动进入 DATA [8]

input CIN;

//加操作的进位进入并位 COUT

assign DATA = A + B + CIN;

assign {COUT, DOUT} = A + B + CIN;

assign COUT = DATA[8];

assign DOUT = DATA[7:0];

endmodule

endmodule

```

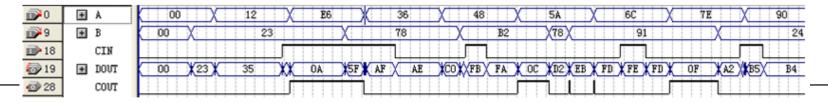

图 2-9 八位加法器仿真波形

### 2.3.2 8位加法器设计及算术操作符应用

图 2-10 8 位加法器 Quartus II 综合之 RTL 电路

表 2-3 算术操作符

| 1 77 - 31 - 1 - 1 - 1 |           |                 |                                   |

|-----------------------|-----------|-----------------|-----------------------------------|

| 逻辑操作符                 | 功能        | 说 明             | 示 例                               |

| +                     | 加         |                 | S = A + B = 8' b00011000          |

| -                     | 减         |                 | S = B - A = 8'b111111110          |

| *                     | 乘         |                 | S = A * B = 8' b10001111 = 2' H8F |

| /                     | 除         | 结果: 小数抛弃        | S = A / 3 = 8' b00000100          |

| %                     | 求余        | 除法求余数           | S = A % 3 = 8' b00000001          |

| 设示例数据是:               | A[3:0]=4' | b1101; B[3:0]=4 | /b1011; 定义s为s[7:0]                |

#### 2.3.3 BCD码加法器设计

```

【例 2-13】

module BCD ADDER (A,B,D);

input [7:0] A,B; output [8:0] D;

wire [4:0] DTO, DT1; reg [8:0] D; reg S;

always@ (DT0)

begin if (DT0[4:0] >= 5'b01010)

//如果低位 BCD 码的和大于等于 10,则使和加上 6,且有进位,使进位标志 S 等于 1。

begin D[3:0] = (DT0[3:0]+4'b0110); S=1'b1; end

else begin D[3:0] = DT0[3:0]; S=1'b0; end

end //否则,将低位值赋予低位 BCD 码 D [3:0]输出,无进位,使进位标志 S 等于 0。

always@ (DT1)

begin if (DT1[4:0] >= 5'b01010)

begin D[7:4] = (DT1[3:0]+4'b0110); D[8]=1'b1; end

else begin D[7:4] = DT1[3:0]; D[8]=1'b0; end

end

assign DT0 = A[3:0] + B[3:0] ; //设没有来自低位的进位。

```

assign DT1 = A[7:4] + B[7:4] + S; //S 是来自低位 BCD 码相加的进位。

endmodule

### 2.3.3 BCD码加法器设计

图 2-11 例 2-13 的仿真波形

表 2-4 不等式操作符

| 等式操作符 | 含义    | 操作示例                                              |

|-------|-------|---------------------------------------------------|

| >     | 大于    | (A < B) = 0; $(A > B) = 1;$                       |

| <     | 小于    | (A < 20) = 1; $(A > 12) = 1;$                     |

| <=    | 小于或等于 | $(A \ge 14) = 0;$ $(A \le 13) = 1;$               |

| >=    | 大于或等于 | 注,以上示例中,设 A= <u>4′</u> B1101 ; B= <u>4′</u> B0110 |

### 2.4.1 参数定义关键词parameter和localparam

```

parameter 标识符名 1 = 表达式或数值 1,标识符名 2 = 表达式或数值 2,...;

```

```

parameter A=15 , B=4'b1011, C=8'hAC;

parameter d=8'b1001_0011 , e=8'sb10101101;

```

integer 标识符 1,标识符 2, ...,标识符 n [msb: lsb];

#### 2.4.2 整数型寄存器类型定义

endmodule

### 2.4.3 for语句用法

for (循环初始值设置表达式; 循环控制条件表达式; 循环控制变量增值表达式) begin 循环体语句结构 end

#### 2.4.4 移位操作符应用法

V >> n 或 V << n

V >>> n 或 V <<< n

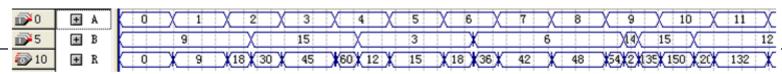

### 2.4.5 两则乘法器设计示例

```

【例 2-14】

【例 2-15】

module MULT4B(R,A,B);

module MULT4B (R,A,B);

parameter S=4;

parameter S=4;

output[2*S:1] R ;

output[2*S:1] R ;

input[S:1] A,B ;

input[S:1] A,B ;

reg[2*S:1] R ;

reg[2*S:1] R, AT; reg[S:1] BT, CT;

integer i;

always @(A,B) begin

always @(A or B)

R=0; AT = \{\{S\{1'B0\}\},A\};

begin

BT = B; CT = S;

for(CT=S; CT>0; CT=CT-1)

R = 0;

for (i=1; i \le s; i=i+1)

begin if(BT[1]) R=R+AT;

if(B[i]) R=R+(A<<(i-1));

AT = AT << 1;

BT = BT >> 1;

end

endmodule

endmodule

end end

```

### 2.4.6 repeat语句用法

repeat(循环次数表达式)

begin 循环体语句结构 end

#### 【例 2-16】

```

module MULT4B(R,A,B);

parameter S=4;

output [2*S:1] R; input [S:1] A,B;

reg [2*S:1] TA,R;

reg [S:1] TB;

always @(A or B) begin

R = 0; TA = A; TB = B;

repeat(S) begin

if(TB[1]) begin R=R+TA; end

TA = TA<<1;

TB = TB>>1;

end

end

endmodule

```

### 2.4.7 while语句用法

while(循环控制条件表达式) begin 循环体语句结构 end

#### 【例 2-17】

```

module MULT4B(A,B,R);

parameter S=4;

input[S:1] A,B;

output[2*S:1] R;

reg[2*S:1] R,AT;

reg[S:1] BT,CT;

always@(A or B) begin

R=0; AT=\{\{S\{1'b0\}\},A\};

BT=B; CT=S;

while (CT>0) begin

if(BT[1]) R=R+AT; else R=R;

begin CT=CT-1; AT=AT<<1; BT=BT>>1;

end

end

end

endmodule

```

### 2.4.8 Verilog循环语句的特点

### 2.4.9 parameter的参数传递功能

#### 【例 2-18】

```

module MULTB (RP,AP,BP);

output[15:0] RP; input[7:0] AP,BP;

MULT4B #(.S(8)) U1(.R(RP), .A(AP), .B(BP));

endmodule

module SUB_E

#(parameter S1=4, parameter S2=5, parameter S3=2)(A,B,C);

SUB_E

```

#(.S1(8), .S2(9), .S3(7)) U1(.C(CP), .A(AP), .B(BP));

### 习 题

图 2-13 含 2 选 1 多路选择器的模块

图 2-14 全减器模块图