|

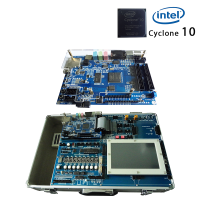

EDA_数字电路实验开发系统

收藏

硬件配置: 1、实验开发系统的组成:主系统(基础平台)+核心板+扩展模块 2、主系统(基础平台)配置 1)、★KX_USB-Blaster2型双功能编程器 2)、★多功能重配置型高效率实验控制电路选择十余种面向不同实验需要的针对FPGA目标芯片的硬件电路连接结构。 3)、8051软核处理器(基于商业级全兼容MCS-51单片机IP核。 4)、★5功能智能逻辑笔:可显示高电平、低电平、中电平、高阻态、脉冲信号。注意有“高阻态”测试功能。 5)、★ 独立的标准时钟频率20个。20MHz、5MHZ 、2.5Mhz、 1.25MHZ、 625kHZ、 65536HZ、 32768HZ 、16384HZ、 4096HZ 、1024HZ 、512HZ 、256HZ、 128HZ 、64HZ、16HZ、 8HZ 4HZ、 2HZ 、1HZ、0.5HZ,从低到高21组时钟可供选择。 6)、电源有自动保护的+5V,+12V、-12V、、+3.3V、2.5V+、1.2V。 7)、8个LED放光二级管,8个拨码开关,扬声器。 8)、DDS信号输出口及幅度、偏移调谐。 9)、6个标准可扩展IO十芯座,1个十四芯座;4组可扩展模块座,1个可扩展DDS模块座、一个可扩展7寸彩屏液晶座; 10)、CPLD3032 11)、尺寸:18*4.7共三块面模板,共720P*3个孔, 12)、★含扫描的智能译码电路模块,12个按键、其中按键可切换成脉冲式、高低电平式、输出4位二进制式电路模式,8数码可切换成直通非译码动态扫描式、智能BCD译码、16进制译码;16个发光二极管(专利); 2、核心适配板 技术指标: 1)、EP4CE10E22C8,10320个可编程逻辑宏单元、423936个SRAM存储单元、2个锁相环)。 2)、4M FPGA专用配置存储器EPCS4。 3)、5个单脉冲按键;扬声器。 4)、20MHz有源晶体振荡器1个和20M无源晶振1个,用于驱动FPGA中的2个锁相环。 5)、VGA、PS/2 鼠标/键盘接口、USB供电输入口。 6)、字符液晶接口;3.3V、2.5V、1.2V电源。 7)、JTAG标准下载口;40X2芯扩展接口。 4、提供的软件资源 1、产品相关的专利证书 1、基本软件:1)Quartus II 13.1正版软件;2)8051单片机IP核;3)Nios II软件; 2、实验配套资源:提供相关的实验指导书,组成原理实验指导书、提供相应PPT课件、PDF教学文档等。提供扩展板原理图。实验指导书及其电子版。 3、★配套教程 潘松 教材 (1)科学出版社《EDA技术实用教程》VHDL/VerilogHDL (2)清华大学出版社出版的《EDA技术与VHDL/VerilongHDL》(可自行订购)。 |